开关电源小课堂(6)—— 系统的电源方案拓扑

前几篇介绍了一些开关电源常用的元器件,以及侧重了解了一下BUCK电路。这次我们先离开一下微观层面,说说宏观上的系统的电源拓扑。不是指BUCK,BOOST等开关拓扑结构,而是电路板系统的电源方案拓扑。正如之前也说过的时钟拓扑那样,任何一个电路板上都会用到电源,在开始设计之初,总要有一个供电方案,比如总的输入电源是多少,经过多少级DCDC或者LDO可以得到我们想要的各个电源网络。

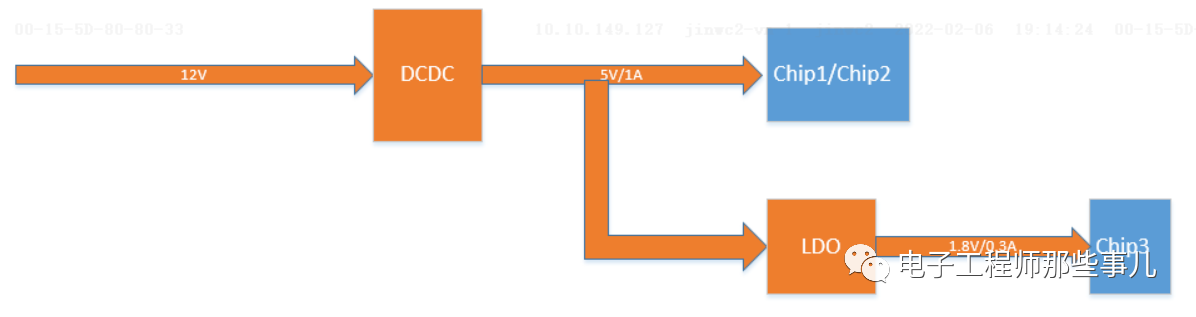

比如下面是一个比较简单的电路系统的电源拓扑:总的12V输入,通过一个DCDC生成5V,给chip1和chip2供电,另外5V还作为一个LDO的输入,生成1.8V,给Chip3供电。Chip1和Chip2需求的5V总电流是1A,Chip3的1.8V电流需求是0.3A。所以DCDC输出5V总电流是1.3A(LDO输入输出电流相等), 总的12V输入的电流就是5*1.3/12=0.54A。当然实际的DCDC效率一般在90%左右,所以实际的总功率需求是12V/0.6A,也就是7.2W。

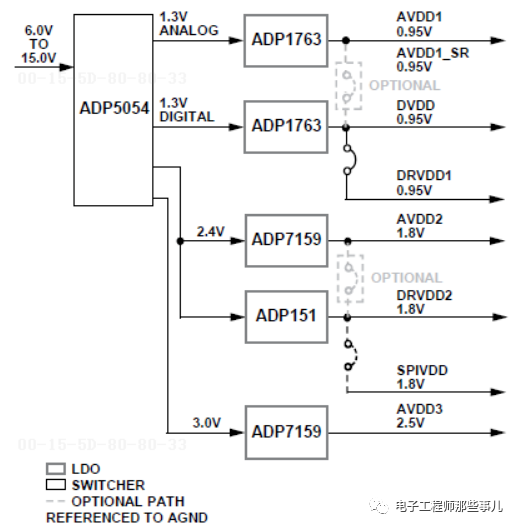

当然这个例子的电源方案只是一个很简单的例子,实际工程中的项目的电源会多很多,一个芯片就需要好多路电源也是比较正常的。比如下图一个拓扑是某一个芯片自身的供电方案,它需要8种电源,其中AVDD1和AVDD1_SR是可以共用一路电源,DVDD和DRVDD1可以共用一路电源,DRVDD2和SPIVDD可以共用一路电源。这还只是一个芯片,如果一个系统中有好几个复杂的芯片,总的电源拓扑要比上面示意图复杂很多了。

电源拓扑设计的时候,主要需要注意几点:

1. LDO输出电流等于输入电流。并且输入电压和输出电压的压差不要过大,以防止LDO热损耗过大。

2. 需要不要忘记DCDC的效率问题,以使得选择的电源芯片留有余量。

3. 注意模拟电路一般需要LDO供电以提供更小的电源噪声,毕竟相比开关电源的开关纹波,LDO的噪声要小很多。数字模拟电路的供电电源分开。

4. 整个系统的电源网络可以合并的尽量合并以减少电源数量,对于一些关键大电流CORE电压,则尽量不要合并。因为这种电源一般瞬态AC电流波动较大,其去耦电容方案都是芯片厂商验证好的,虽然合并可能会增加电源铜皮面积和去耦电容的总数量,但这未必是好事。

5. 基准源电压只能提供专用的VREF参考电压用,因为其电流非常小,不能用作给其他普通电源供电使用。

最后最重要的一条就是留够余量。

图文转自公众号:电子工程师那些事儿